12月30日,据韩国媒体报道,三星电子正在研发一种名为FOWLP-SbS的先进封装技术,该技术有望显著提升Exynos系列芯片的散热性能。其中SbS意为并排布局,指关键芯片组件在封装中以并列方式排列。

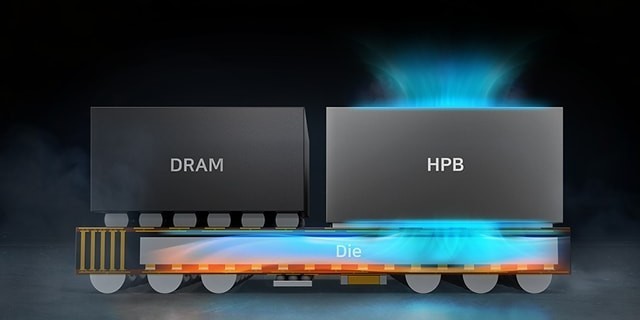

目前,高端移动处理器如Exynos 2600普遍采用在SoC裸片上方堆叠封装DRAM内存的设计,这种结构有助于缩短信号走线并节省空间。此外,Exynos 2600还在SoC裸片上应用了HPB散热结构,使热阻最多降低16%,有效改善了芯片的热管理能力。

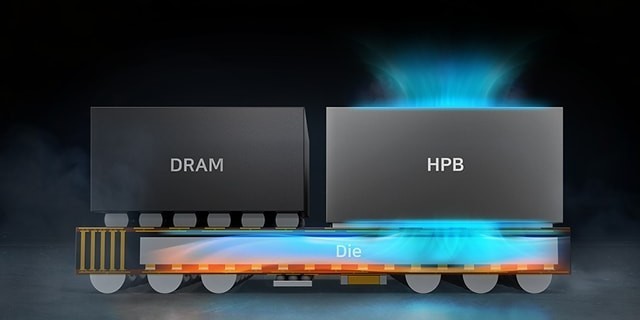

而在FOWLP-SbS封装方案中,SoC裸片与DRAM不再采用垂直堆叠,而是改为水平并排放置,二者上方统一覆盖HPB散热层。这一设计扩大了SoC与散热结构的接触面积,从而进一步提升散热效率。同时,SoC与DRAM之间预计将通过混合键合技术实现高密度、短距离互连,保障信号传输性能。

分析指出,FOWLP-SbS技术具备降低整体封装厚度的优势,允许使用更厚的SoC和DRAM裸片,有利于电源布线的优化设计。然而,该方案也存在占用更大平面空间的不足。因此,该技术可能优先应用于对机身厚度敏感但内部横向空间相对充裕的折叠屏设备中。

本文属于原创文章,如若转载,请注明来源:三星研发FOWLP-SbS封装技术提升Exynos芯片散热性能https://mobile.zol.com.cn/1109/11093045.html